我胡汉三又回来了 ~

差点账号密码全忘了~

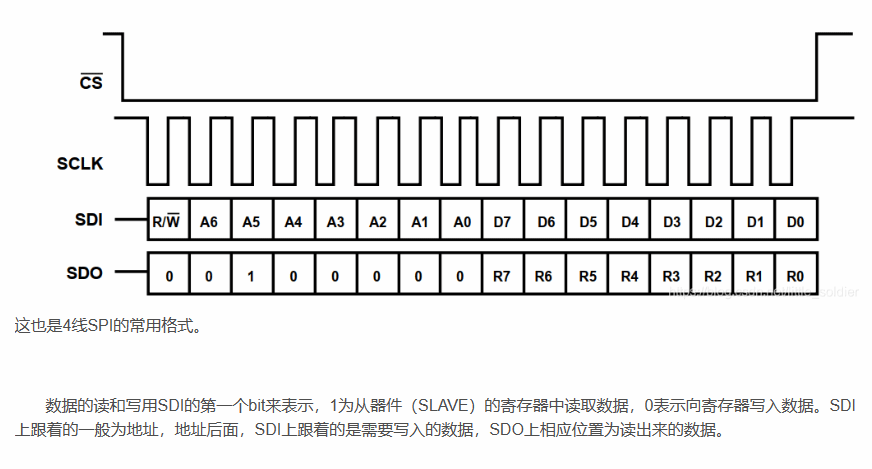

最近在忙FPGA与7043SPi通讯的事情,其中FPGA里的spi是自己用的microblaze中的AXI Quad SPI核,他的标准时序是这样的

他需要四根线,分别是片选信号(CS)、时钟(SCLK)、SDI(主机输出,从机输入)、SDO(主机输入、从机输出)。

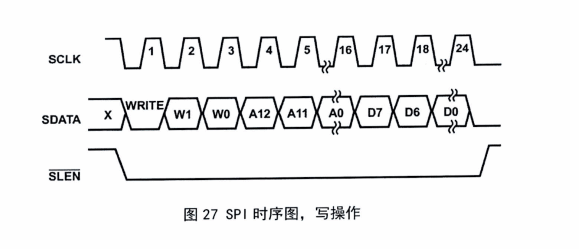

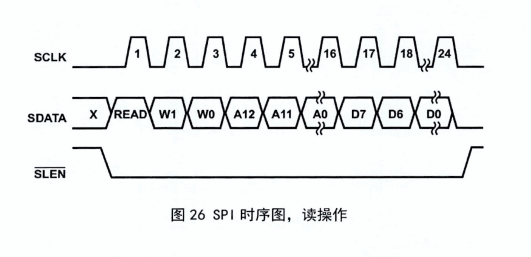

而7043的SPI时序图是这样的:

相信你们已经发现了,他只有三根线片选(SLEN)、时钟(SCLK)、数据(SDATA)。

所以很长一段时间,SPI只能读不能写。

咋办,咋办我网上搜索过,有个很复杂的办法,搞了,没用(说实话没看懂),链接如下:

https://www.eet-china.com/mp/a34485.html

无果,想着自己写驱动吧,奈何能力不够,时钟与片选信号的时序一直不对。

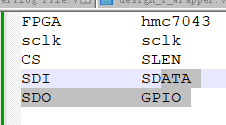

最终上了ADI官方论坛(一开始没想这个,因为我用的国产芯片),终于找到了方法!!!7043的IO口可以设置成SDATA的数据接收拷贝,从而让全双工的SPI能够接收半双工的数据。

具体操作方法如下:

https://ez.analog.com/clock_and_timing/f/q-a/568857/about-hmc7043-spi-interface

先复位,然后将寄存器0x46、0x50、0x56分别配置为0、7、3。

硬件上这样接:

然后就能直接用了~

赏个积分吧~~~

不懂 下一个

不懂,下一个

脑袋好痒